Get a new board, usually we can't wait to run a test demo to see the effect, but please believe that this is a "novice" feature. We are no longer young, and there is no need to "recklessly" toss the board. Returning to rationality, then I suggest that you may wish to take a look at the schematic diagram first, then compare the board with the actual object, simply digest the whole circuit, and figure out the specific usage and precautions of the onboard jumper, power socket, etc., so as not to stage the "high voltage." The tragedy of smoking.

The schematic of the Nexys3 is available on the official website of Digilent (download address:). For schematics, you usually need a certain amount of hardware skills to be able to easily see. Of course, the general development board will be equipped with a more detailed circuit description (this development board can be referenced), it is recommended that you may wish to look at it first, and then digest the schematic.

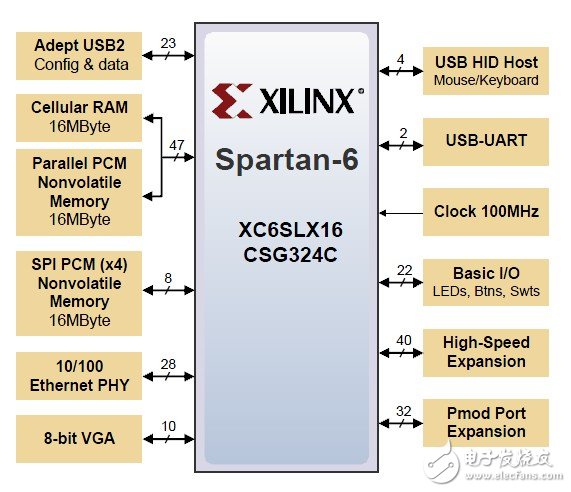

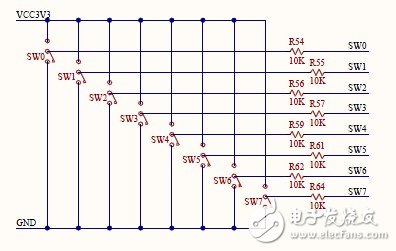

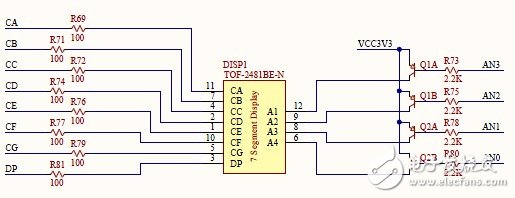

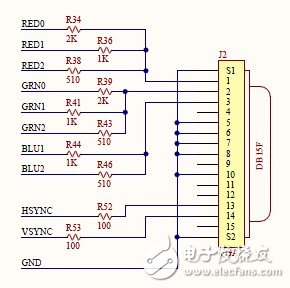

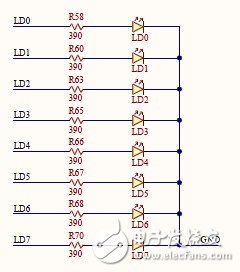

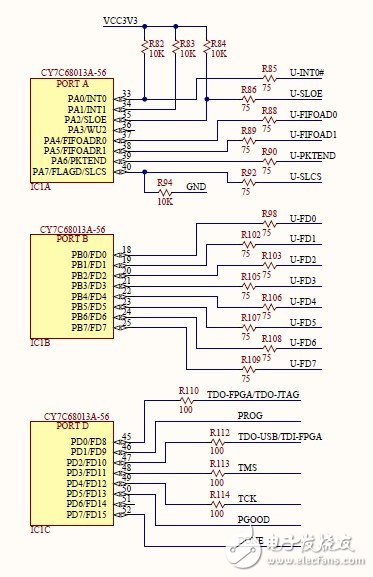

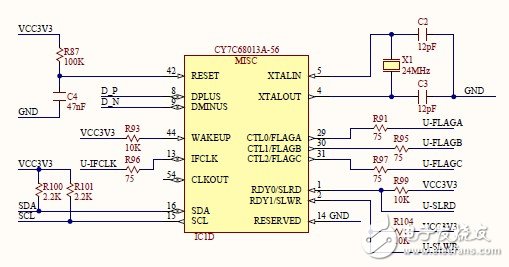

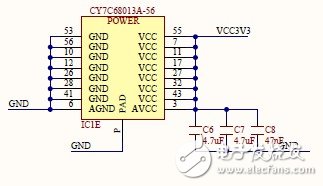

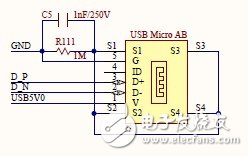

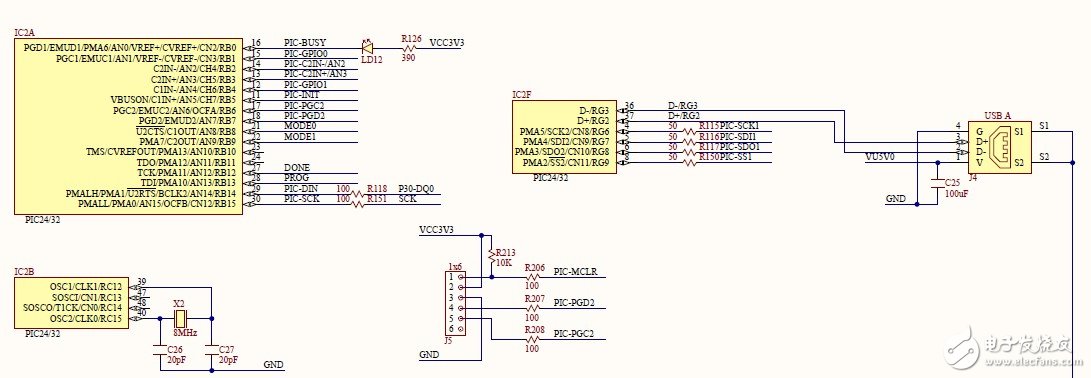

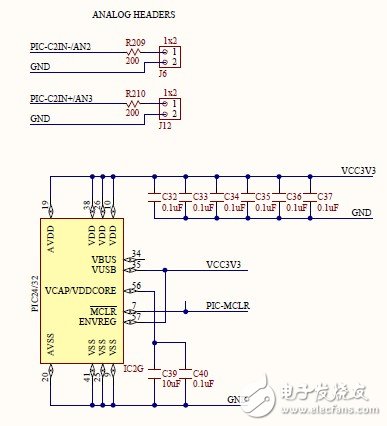

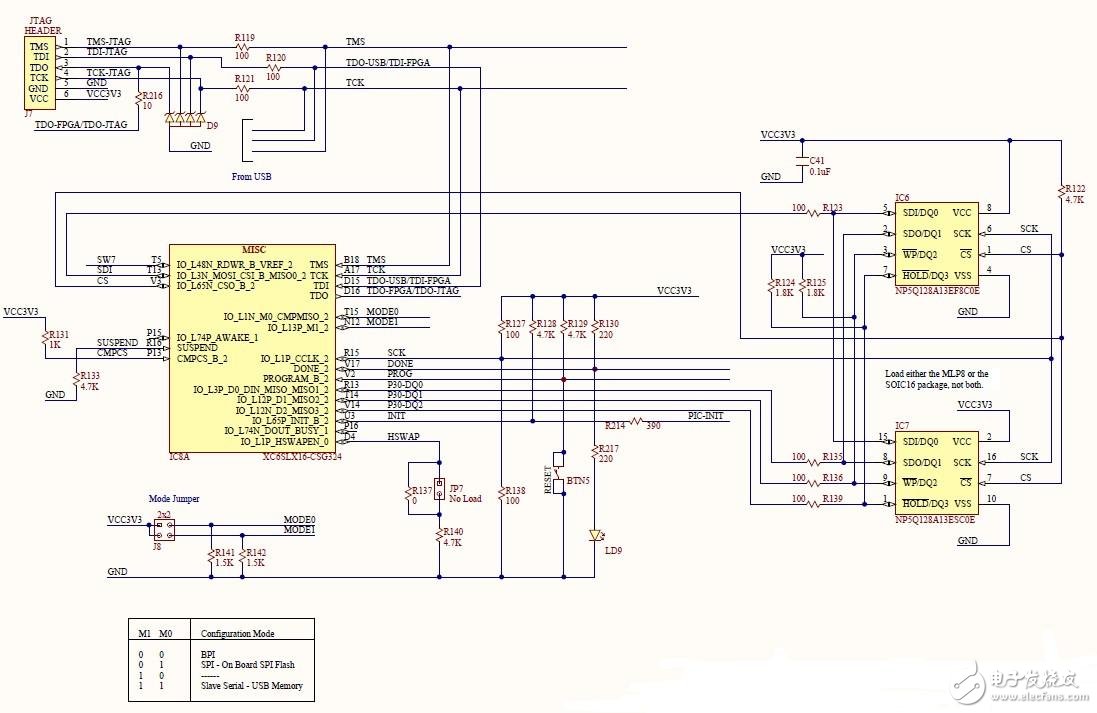

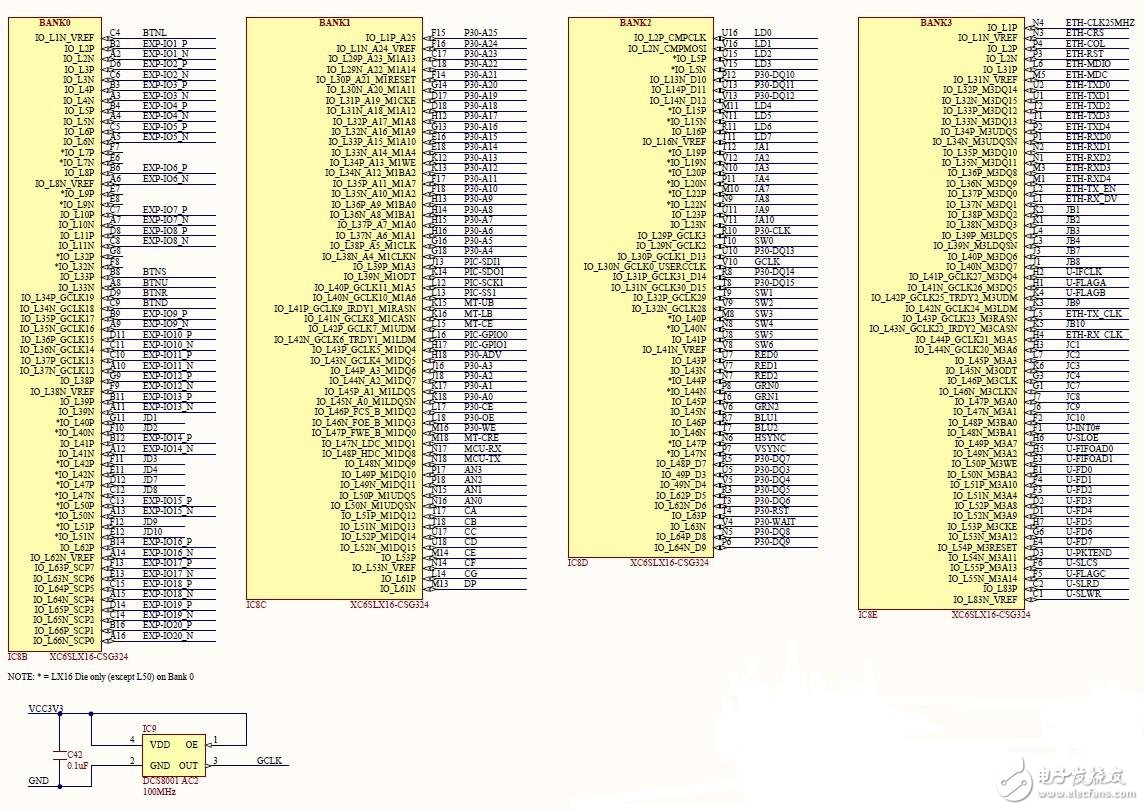

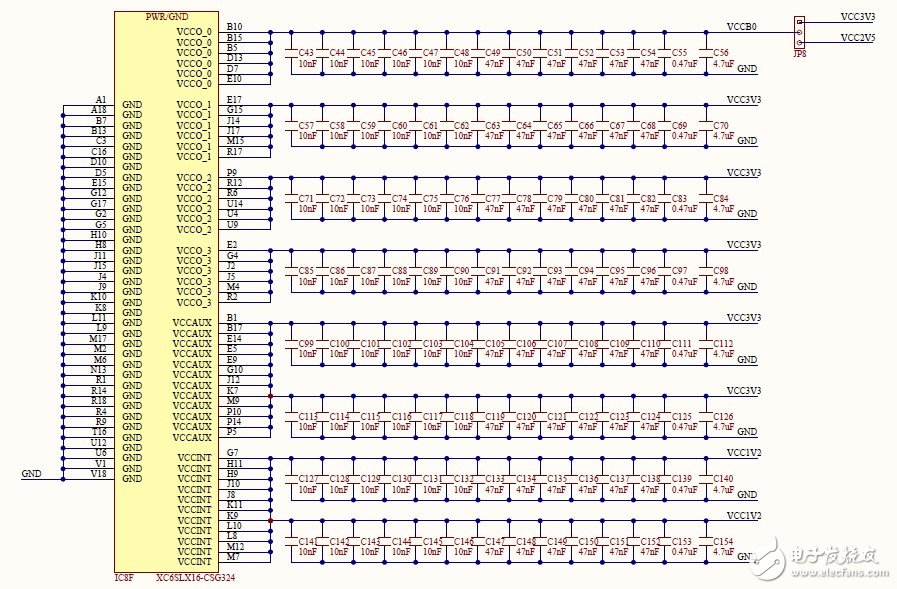

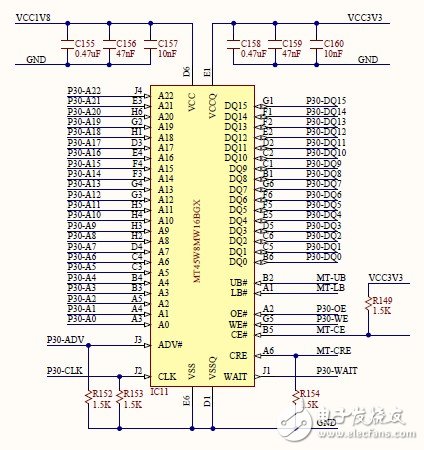

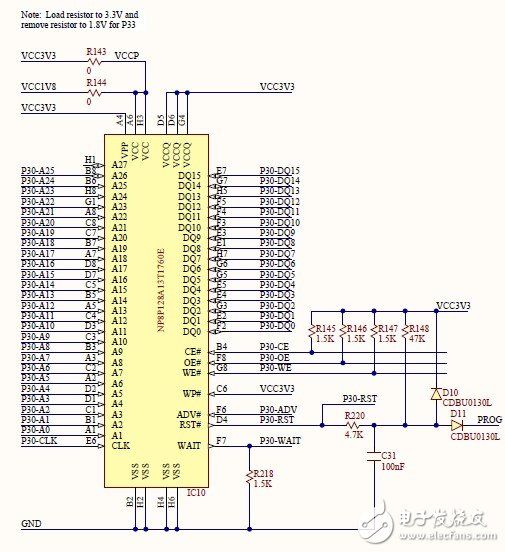

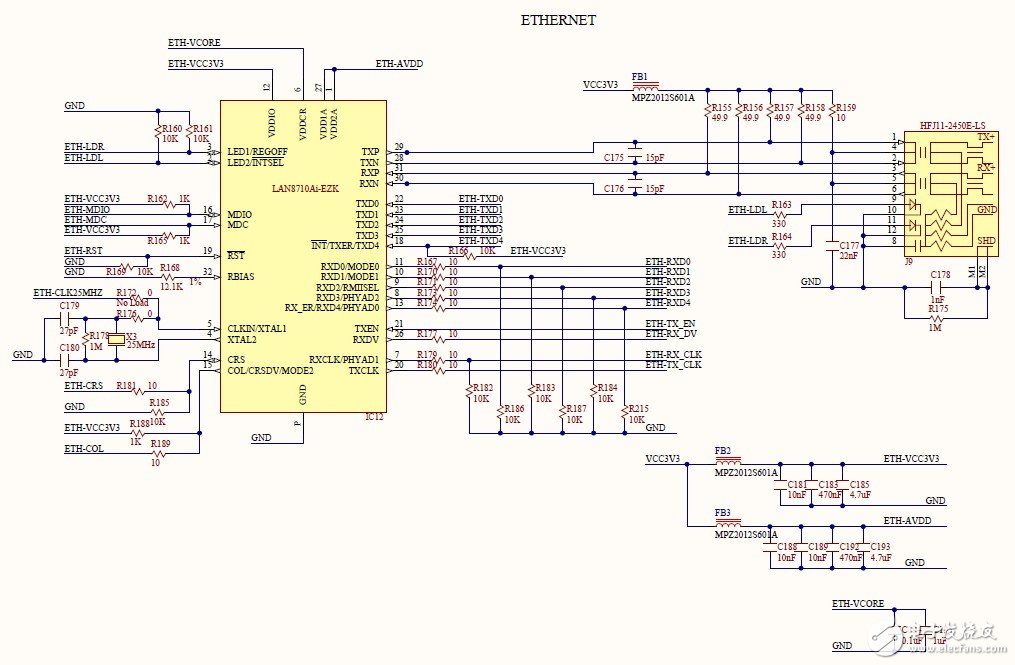

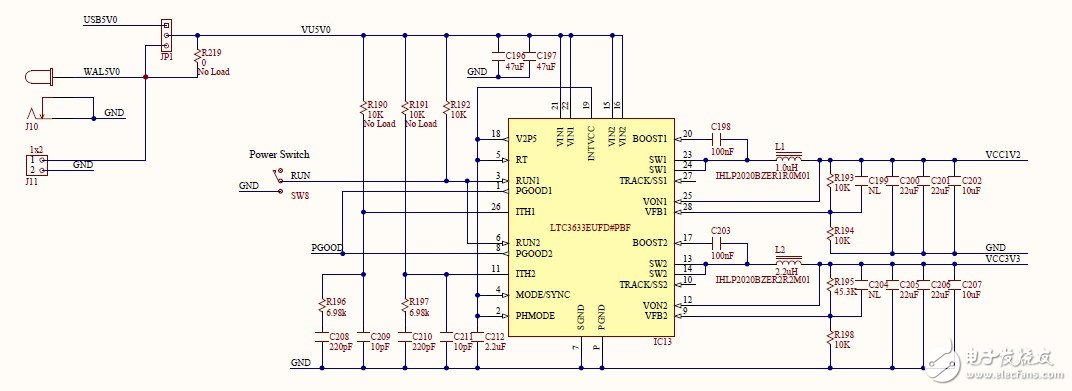

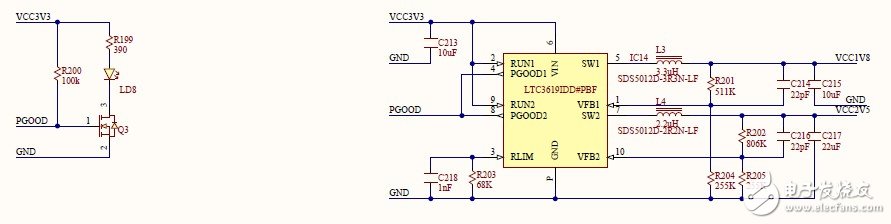

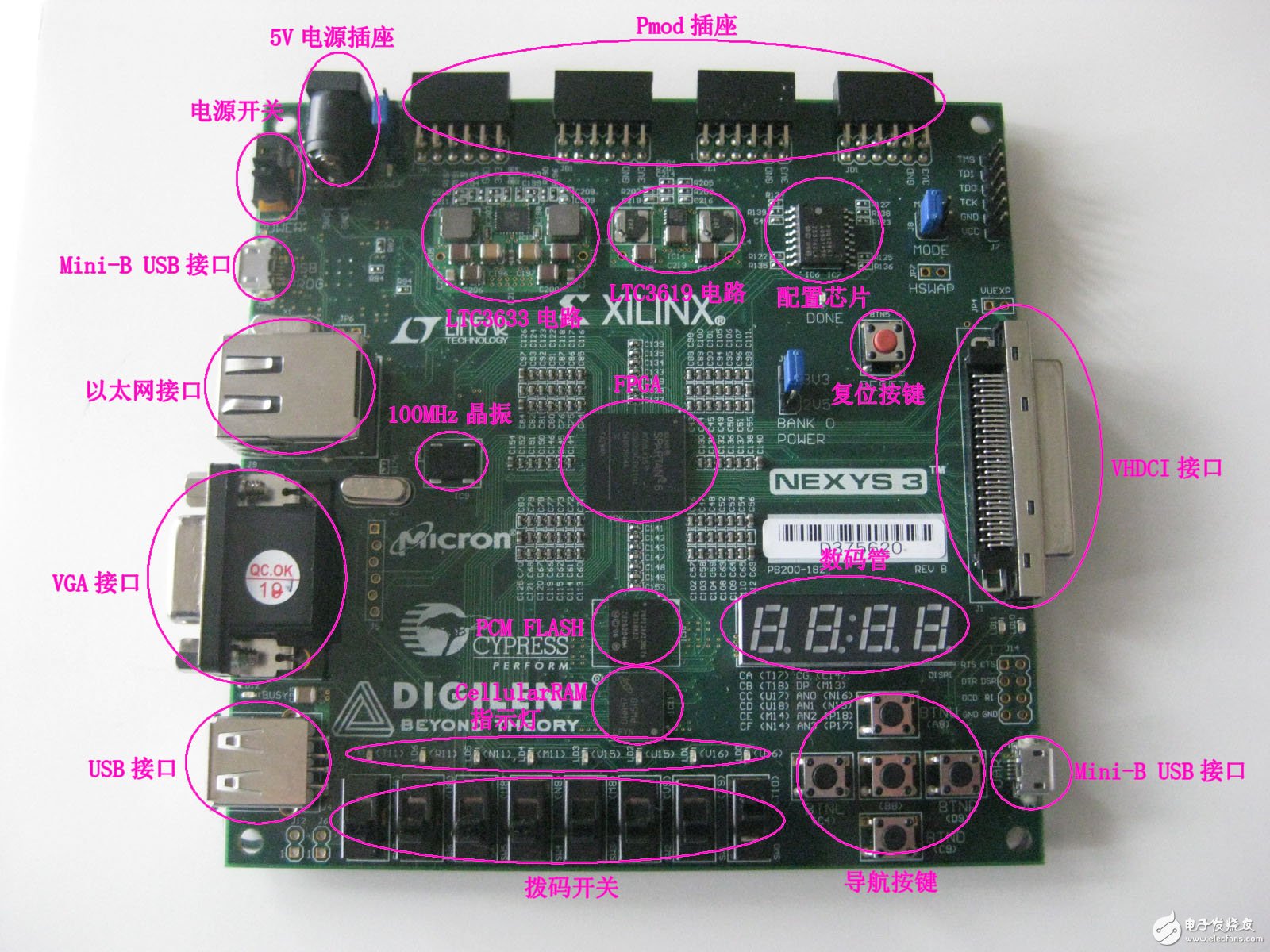

The overall hardware architecture of the Nexys3 board is illustrated in Nexys3_rm.pdf (reference manual), as shown in Figure 1. The XC6SLX16 device around the main chip Spartan-6 has a wealth of onboard peripherals such as Cellular RAM, parallel PCM nonvolatile memory, SPI interface PCM nonvolatile memory, 10/100 Ethernet physical layer interface, 8-bit VGA interface, USB HID host, USB-UART bridge chip and some basic IO peripherals (indicators, buttons, switches, etc.), in addition to FPGA USB download configuration circuit, 100MHz working clock and other expansion interface sockets.

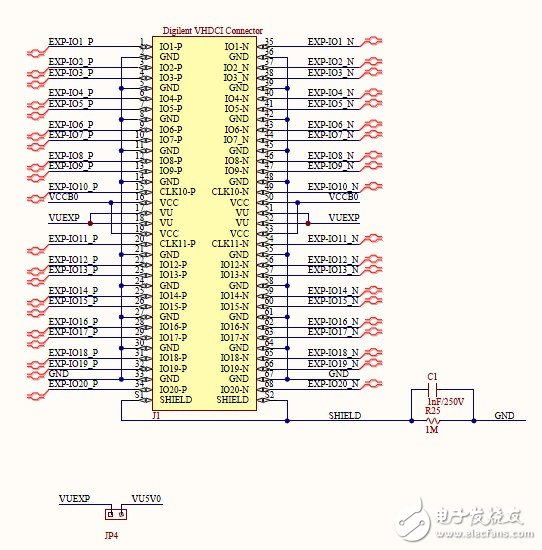

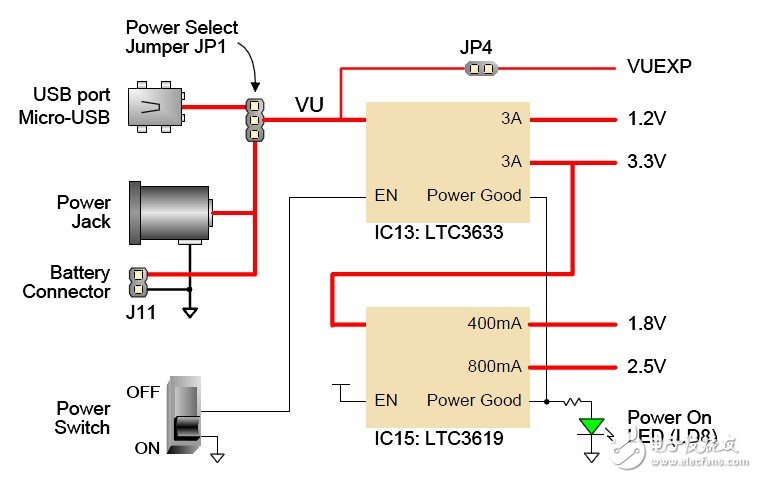

J1 in Page1 is a high-speed VHDCI socket interface, as shown in Figure 2. It is not difficult to conclude from the schematic diagram and signal naming of the schematic that the signals directly derived from the FPGA should be high-speed serial differential pairs. In addition, we need to note that JP4 can be used to short-circuit the power supply VUEXP introduced by J1 and the on-board power supply VU5V0. In other words, if the 5V power supply introduced by J1 is used, JP4 can be shorted.

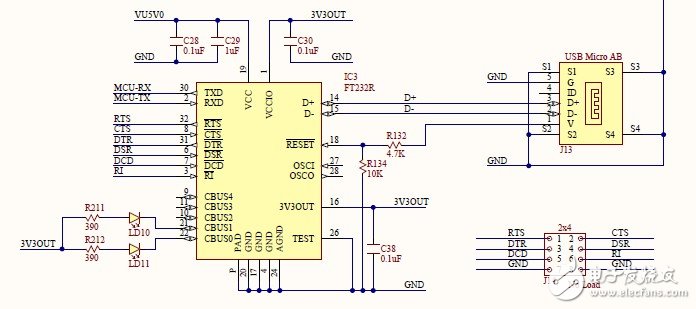

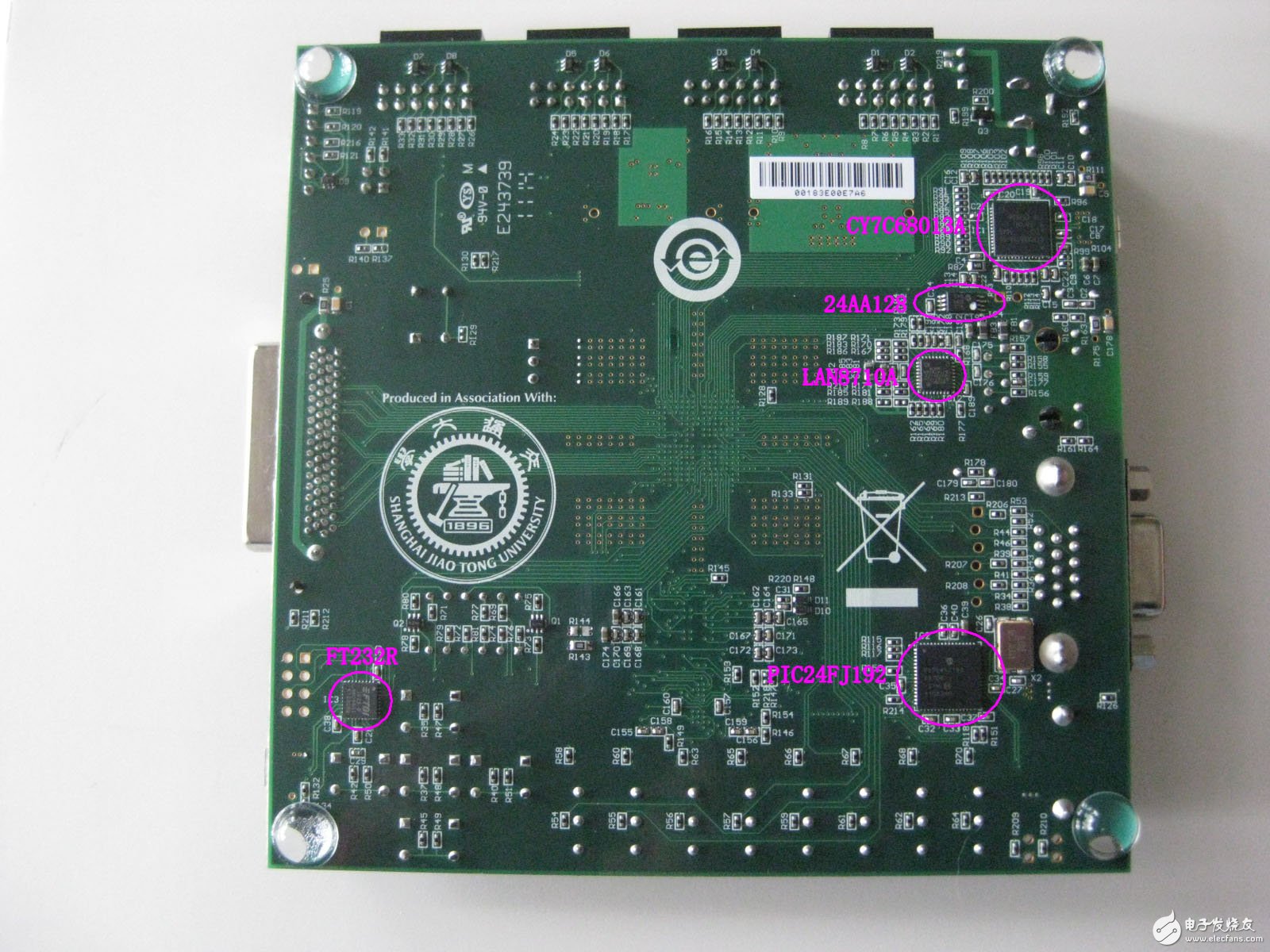

As shown in Figure 16, the FPGA is also connected to a RS232-USB bridge chip FT232. The chip provides a standard set of RS232 interfaces (J14 also provides additional extensions for these interfaces) to connect to the FPGA, and the other end can communicate as a USB protocol interface.

Anatomy of the board

Seeing more of the schematics, it is inevitable that aesthetic fatigue. Let's take a break. The privileged classmates will not talk nonsense. According to the previous schematic diagram, as shown in Figure 26 and Figure 27, the main chip and connectors are taken out one by one.

The cables are for the solar system.

Solar Cable,Pv Wire,Solar Dc Cable,Dc Wire For Solar Panels

NANTONG RONGCHANG IMPORT&EXPORT CO.,LTD , https://www.ergsolarcn.com