Abstract: The main functions, manufacturing processes and tests of the L82C37A programmable DMA controller are described. The basic circuit and design method are briefly introduced.

1 OverviewThe L82C37A Programmable DMA Controller is a high performance programmable direct access controller that allows direct data transfer between memory and peripherals without CPU intervention. In a microcomputer system, the data transfer rate of a single or multiple I/O devices of the system can be greatly improved by using DMA operations.

The circuit is fabricated in a 2.0μm silicon gate CMOS all-ion implant process with an integrated 13500 tube position and a chip area of ​​25.12mm2 in a DIP 40 PIN ceramic package.

The circuit has the following features:

Compatible with NMOS 82C37A;

Has four programmable independent DMA channels, each with automatic initialization capability;

Can transfer from memory to memory;

There are four basic working methods and three transmission methods;

Arbitrarily expand the number of DMA channels;

Each channel has a 64k address and a 64k byte count space;

The maximum data transfer rate can reach 4MB/sec.

Low power static CMOS design, IDDSB = 10μA;

Compatible with TTL;

Single 5V power supply;

Operating frequency 8MHz;

Operating temperature range -55 ° C ~ +125 ° C.

2 Logical structure and function 2.1 L82C37A main functionThe main functions of the L82C37A are as follows:

(1) The circuit has four independent DMA channels;

(2) DMA requests for each channel can be allowed and disabled separately;

(3) The DMA request priority of each channel has a fixed mode and a cyclic mode;

(4) The maximum length of 64k bytes of data transmitted once per channel can be transmitted between the memory and the peripherals, or can be transmitted in two intervals of the memory;

(5) There are four DMA transmission modes: 1 single-byte transmission mode; 2 data block transmission mode; 3 request transmission mode; 4 cascade connection mode. In each mode, after receiving the peripheral request signal DREQ, the response signal DACK can be sent to the peripheral to occupy the bus for DMA transfer. Each time a byte is transmitted, the address pointer is modified once, and when the number of bytes to be transmitted is sent out, the terminal counting pulse TC is issued, and the transmission is terminated or re-initialized;

(6) Allow the peripheral to end the DMA transfer or reinitialize with the EOP signal;

(7) L82C37A can be cascaded and the number of channels can be expanded arbitrarily.

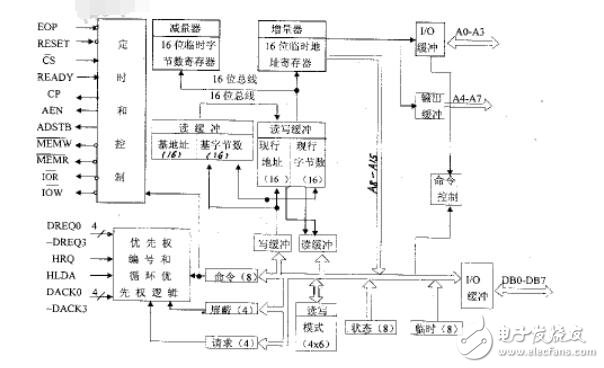

2.2 L82C37A logical structureThe logic function of L82C37A is more complicated, and its logic block diagram is shown in Figure 1. The channel portion of the figure only shows one channel, that is, each channel has a base address register (16 bits), a base byte count counter (16 bits), a current address register (16 bits), and the current byte. Number counter (16 bits), each channel has a 6-bit mode register to control different operating modes.

Figure 1 L82C37A logic block diagram

The structure of the L82C37A contains three basic control logic blocks.

Timing Control Logic Block: Generates internal timing and external signals required for DMA requests, DMA transfers, and DMA termination based on the programmed DMA mode of operation.

Program Command Control Block: The CPU program decodes a given command word and mode control word to determine the type of DMA service prior to servicing the DMA request.

Priority Encoding Logic: Priority encoding of the simultaneously requested channel to determine which channel has the highest priority, and the priority can be fixed or cyclic.

In addition, the L82C37A's data leads have a tri-state buffer that can be used as well as the bus.

2.3 L82C37A work cycleThe L82C37A has two main duty cycles, the idle period and the active period, each of which consists of several clock cycles.

(1) Idle period

After completing a DMA service, the L82C37A will enter the idle cycle to execute the SI state if there is no new DMA request, or after a primary clear or a hardware reset. It samples the channel's request line DREQ every clock cycle, and it will always be in the SI state before it receives the DREQ.

In this state, the CPU can query its status or program it. If  The CPU can read and write to it, and can read/write its base address, base byte number, current address, current byte number and other registers. At this point, you need to pass the data bus and address bus and

The CPU can read and write to it, and can read/write its base address, base byte number, current address, current byte number and other registers. At this point, you need to pass the data bus and address bus and  And to select the register and rewrite the data. Since these four sets of registers are all 16 bits and the data bus is 8 bits, it is controlled by the internal high/low bit registers, dividing the data into upper 8 bits and lower 8 bits, and writing them twice. There are also some software commands that do not pass the data bus, only by the address A0-A3 and

And to select the register and rewrite the data. Since these four sets of registers are all 16 bits and the data bus is 8 bits, it is controlled by the internal high/low bit registers, dividing the data into upper 8 bits and lower 8 bits, and writing them twice. There are also some software commands that do not pass the data bus, only by the address A0-A3 and  The decoding of the signal is set.

The decoding of the signal is set.

(2) Effective period

When the peripheral or CPU issues a DMA request, it will jump out of the SI state and enter the first state S0 of the DMA service. At this time, although SREQ is received and HRQ is issued, after receiving the HLDA signal from the CPU, the L82C37A enters the working state composed of S1-S3. If the peripheral working speed is slow, the DMA transfer cannot be completed before the S4 state. When the READY line is used, the SW state can be inserted between S2 or S3 and S4 until the end of this transmission. The SW state is a wait period, mainly to accommodate slow peripherals to extend the transmission time.

In the memory-to-memory transfer, memory read and write operations are required, so each transfer requires 8 clock cycles, of which 4 cycles S11-S14 complete the memory read and the other 4 cycles S21-S24 complete the memory write operation.

Wholesale OEM Available 800 Puffs Electronic Cigarette Vape Disposable

This Elegant pre-filled disposable pod system with slim body featured with advantages as below:

1, Under Voltage Protection

2, 3.6V Constant Output

3, LED Light Battery Indicator

4, 10 Seconds Cut-Off Protection

5, Short-Circuit Protection

6, Over Temperature Protection

2ml energy fruit flavor e-juice, 450mAh battery build-in, small in size, let you enjoy amazing vaping experience on the go.

Flavors:

1. Fizzy Cola

2. Ice Grape

3. Ice Lychee

4. Ice Watermelon

5. Mango Butter

6. Mango Smoothie

7. Nutty Tobacco

8. Strawberry Milkshake

Electronic cigarette,e-cigarette,vapes e cigarette electronic,disposable vape,vape pen

Shenzhen Axiswell Technology Co., Ltd , https://www.medhealthycare.com