Jump points are an important concept in all important timing analysis tools. The trip point is used by the timing analysis tool to calculate the delay and transition values ​​on the design node. Some different meanings of the trip point may be ignored by the timing analysis engineer. This may cause problems in the later stages of SOC design, that is, when timing signatures. It is very important that the back-end design engineer knows the concept of the transition point and its meaning. This is where the purpose of this article is.

1. Jump point definition:

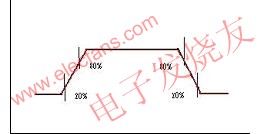

The trip point can be defined as a percentage of the logic high level as a reference for measuring the slew rate and the delay value. Figure 1(a) shows the slew rate jump point.

Figure 1 (a)

Figure 1(b) shows the delay trip point.

Figure 1 (b)

The trip point is used to describe the pin transition value characteristics of a standard cell or a hard block (IP), etc., while checking the SoC timing. Usually the value of the trip point is mentioned in the timing model (free form), which is used by the timing analysis tool to calculate the delay and slew rate.

2. How to fix the jump point:

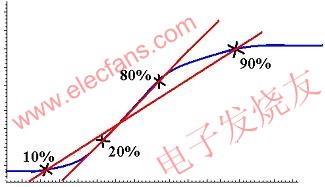

When describing standard cell or hard module (IP) features, the trip point is fixed for a particular technology node. The purpose of fixing the trip point is to ensure that the measured delay/swing rate is close to the actual waveform. As shown in Fig. 2(a), when the trip point is in the linear region (20%-80%) of the switching waveform, the slew rate value is more optimistic than in the nonlinear region (10%-90%).

Figure 2 (a)

Normally, the timing delay calculated by the timing tool is closer to the Spice result when the transition trip point is in the linear region.

At the same time, the voltage threshold (Vt) characteristic of the transistor plays an important role in determining the trip point because the output waveform is linearized after the input voltage exceeds the Vt value of the transistor [1].

The delay threshold is fixed in the linear region of the input and output waveforms. As long as the delay trip point is in the linear part of the waveform, it does not matter whether the delay trip point is 20-80 or 50-50.

3. Jumping point syntax mentioned in free format [2]

Below is a snapshot of a typical timing model (.liberty file) to indicate which trip point is being used.

Input_threshold_pct_rise:50;

Input_threshold_pct_fall:50;

Output_threshold_pct_rise:50;

Output_threshold_pct_fall:50;

Slew_lower_threshold_pct_rise:20;

Slew_lower_threshold_pct_fall:20;

Slew_upper_threshold_pct_rise:80;

Slew_upper_threshold_pct_fall:80;

4. How does the timing tool handle the jump point to calculate the delay?

a) When the jump point is the same for the interface:

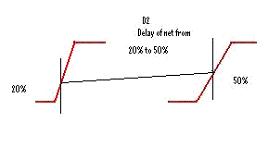

Figure 3(a) depicts the situation when the driver and load have the same latency threshold.

In the example given, both are 50%.

Figure 3 (a)

At this point, considering the slew rate degradation (caused by the network), the timing tool calculates the time difference between the driver's 50% logic high and the load reaching its 50% logic high.

A similar explanation applies equally to the falling signal and delay produced by the input and output of a particular unit. The slew rate value is calculated from the variables mentioned in .lib.

b) when the jump point is for an interface and not simultaneously

(i) 20% to 50%:

Figure 4(a) depicts the case where the driver delay trip point is 20% and the load cell trip point is 50%.

In this case, the driver's signal quickly reaches its delay trip point value compared to the load signal. Therefore, the network latency of such interfaces will be greater than the delay in the case where the driver also reaches 50% [Fig. 3(a)].

Figure 4 (a)

Timing tools can calculate additional delays on the network by linear or non-linear expansion.

(ii) 50% to 20%

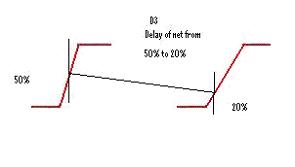

Figure 4(b) depicts the case where the driver trip point is 50% and the load cell has a trip point of 20%.

In this case, the load's signal will reach its delay trip point earlier than the drive signal. This situation is handled by the timing tool by means of extension (linear or non-linear).

Figure 4(b)

It should be noted here that in this case, the extension will cause "negative delay".

It should be noted that although the real world cannot traverse backwards in the time domain, the timing tool needs to take this delay into account, so that from the starting point (in this case, the input pin of the drive unit) to the termination point ( In this example, the overall path delay of the output pin of the load cell is close to the real world time delay (Spice).

5. Other issues related to the jump point:

(i) Negative delay in SDF: The negative delay generated after the extension by the timing tool is replicated in standard delay format (SDF) for gate level simulation. This is not expected because the gate level simulator cannot handle negative delays.

They either flag the error message or indicate zero latency for such cases. As a workaround, you can write a script (Appendix A) that increases (or decreases) the load cell (or drive unit) delay based on the calculated negative delay.

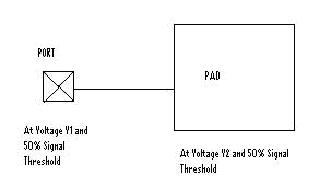

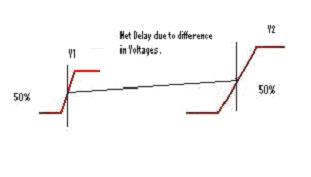

(ii) Additional delay between port and IO unit:

Usually the timing tool reports the latency of the port to the I/O unit. On the silicon wafer, the network appears as a bond wire outside the chip. Therefore, the physical information of the network cannot be quantified.

The timing tool provides a latency report for such networks. Reasons include:

a) Since no timing model is available for the port, the timing tool calculates the delay using user-defined or default trip points and voltage levels.

b) Because there is a difference between the voltage level values ​​of the trip point and the wrTI/O unit trip point of the port. Figure 5 (a) and Figure 5 (b) describe such a situation.

Figure 5 (a)

Figure 5(b)

To overcome this situation, you can do the following:

1) Define operating conditions for the same port as the I/O unit's port.

2) Write a script to annotate zero latency for such a network.

(iii) Library with missing trip points

If we have a time series model that does not contain trip point thresholds or voltage level values, the delay from/to the interface to such models may be incorrect. Because the timing tool uses the default values ​​for the trip point and voltage level, these paths are analyzed. As a workaround, the user should define the jump point after consulting the person in charge of the library.

6. What if you don't expand through the timing tool: Intense. This can cause chip failures because the latency calculated using the timing tool is not close to the Spice value. If you can perform a Spice analysis for a different interface with a different jumping point, it should be a good method of operation.

If you use the same jump point for all the models (hard modules) used in the SOC, it should be a good method of operation.

This completely eliminates the problems caused by different thresholds.

7.Spice partnership:

Spice analysis of multiple threshold paths is a good way to increase confidence and solve timing problems.

Although in the Spice world, the threshold does not actually exist. They are used in timing models to simplify timing analysis tools.

The timing tool provides an option to copy the list of spice nets for a particular timing path. In addition to the spice net list, the stimulus file containing the input vector is also copied. The copied spice net list may not contain a list of spice nets for standard cells and/or hard modules in the timing path.

The Spice simulation tool reads a list of replicated spice nets and a list of standard unit/hard modules' spice networks, and then provides stimulus files to simulate important paths.

You need to analyze the generated waveform to see if the path meets the timing requirements. When measuring the delay and transition values ​​of such paths in SPICE, keep in mind that the same trip points as those mentioned in the timing model are used.

8. Extension type:

Most industry standard tools use linear or nonlinear extensions as their way of working

a) Linear expansion: In this method, the tool assumes a linear slope of different thresholds.

This method uses the concept of a similar triangle to extend the delay of the driver to the load unit.

b) Nonlinear expansion: At this point, the tool uses a current source model to define the ramp. This requires complex mathematical equations to calculate the delay.

In summary, this article begins with a definition of a trip point and then explains how to fix the trip point for a particular technology library. This article then discusses how the timing tool interprets the trip point and the problems that can arise when the driver is different from the load cell trip point.

Appendix A: Scripts for Negative Interconnect Latency in SDF

#!/usr/local/bin/perl

Print "***************RUNNING PERL SCRIPT negaTIvedelinsdf_assarray.pl****";

If (!exists $ARGV[0] || !exists $ARGV[1]) { print "USAGE:: negaTIvedelinsdf_assarray.pl "; exit;(corrected)>

}

Open(FILEA,$ARGV[0]) || die ("ERROR:: SDF file $ARGV[0] cannot be opened for reADIng");

Open(file1, ">$ARGV[1]") || die ("ERROR:: file $ARGV[1] cannot be opened for wriTIng");

While()

{ $line = $_;

$line1 = $line;

$line =~ s/^\s+//g ;

If ( $line =~ "INTERCONNECT.*-[0-9]") ######## FINDING NEGATIVE INTERCONNECT ######

{

@array1 = split(/\s+/,$line);

$count = @array1;

If ($count == 4){ ## To accont for the fact that only one INTERCONNECT triplet is present

$array1[$count]= $array1[$count-1];

$count = $count + 1;

}

For($i=0;$i<= $count -3;$i++)

{print file1 "$array1[$i] ";}

$value2 = $array1[$count -1];

$value1 = $array1[$count -2];

$instance_name = $array1[2];

@instance = split(/\//,$instance_name);

$count2 = @instance;

$pin_name = $instance[$count2 -1]; ####### GETTING LOAD INSTANCE PIN NAME ###############

$instance_name =~ s/\/[^(.*\/)][A-Z0-9a-z_\[0-9\]+]*$//g; ####### GETTING LOAD INSTANCE NAME ###############

If( $value1 =~ "::")

{ $value1 =~ s/[()]//g;

@correct_value1 = split(/::/,$value1);

$load_correct_value1_0{$instance_name} = $correct_value1[0];

$load_correct_value1_1{$instance_name} = $correct_value1[1];

If($correct_value1[0] <= -0.0) #####NEGATIVE CHANGED TO ZERO DELAY######

{$correct_value1[0] = "0.000";}

If($correct_value1[1] <= -0.0)

{$correct_value1[1] = "0.000";}

Print file1 "($correct_value1[0]::$correct_value1[1])";

}

Elsif( $value1 =~ ":[^:]")

{ $value1 =~ s/[()]//g;

@correct_value1 = split(/:/,$value1);

$load_correct_value1_0{$instance_name} = $correct_value1[0];

$load_correct_value1_1{$instance_name} = $correct_value1[1];

$load_correct_value1_2{$instance_name} = $correct_value1[2];

If($correct_value1[0] <= -0.0) #####NEGATIVE CHANGED TO ZERO DELAY######

{$correct_value1[0] = "0.000";}

If($correct_value1[1] <= -0.0)

{$correct_value1[1] = "0.000";}

If($correct_value1[2] <= -0.0)

{$correct_value1[2] = "0.000";}

Print file1 "($correct_value1[0]:$correct_value1[1]:$correct_value1[2])";

}

Else{print file1 "$value1 ";}

If( $value2 =~ "::")

{ $value2 =~ s/[()]//g;

@correct_value2 = split(/::/,$value2);

$load_correct_value2_0{$instance_name} = $correct_value2[0]; ########NEGATIVE CHANGED TO ZERO DELAY#####

$load_correct_value2_1{$instance_name} = $correct_value2[1];

If($correct_value2[0] <= -0.0)

{$correct_value2[0] = "0.000";}

If($correct_value2[1] <= -0.0)

{$correct_value2[1] = "0.000";}

If ($correct_value1[0] == $correct_value2[0] && $correct_value1[1] == $correct_value2[1] ) { # Print these values ​​only if they are differnet from the already printed values ​​for the INTERCONNECT

Print file1 ")";

} else {

Print file1 " ($correct_value2[0]::$correct_value2[1]))";

}

}

Elsif( $value2 =~ ":[^:]")

{ $value2 =~ s/[()]//g;

@correct_value2 = split(/:/,$value2);

$load_correct_value2_0{$instance_name} = $correct_value2[0]; ########NEGATIVE CHANGED TO ZERO DELAY#####

$load_correct_value2_1{$instance_name} = $correct_value2[1];

$load_correct_value2_2{$instance_name} = $correct_value2[2];

If($correct_value2[0] <= -0.0)

{$correct_value2[0] = "0.000";}

If($correct_value2[1] <= -0.0)

{$correct_value2[1] = "0.000";}

If($correct_value2[2] <= -0.0)

{$correct_value2[2] = "0.000";}

If ($correct_value1[0] == $correct_value2[0] && $correct_value1[1] == $correct_value2[1] && $correct_value1[2] == $correct_value2[2]) { # Print these values ​​only if they are Differnet from the already printed values ​​for the INTERCONNECT

Print file1 ")";

} else {

Print file1 " ($correct_value2[0]:$correct_value2[1]:$correct_value2[2]))";

}

}

$load_instance{$instance_name} = $instance_name; ##SAVE ALL LOAD INSTACES FOR NEG DELAY IN THE ASSOCIATIVE ARRAY##

$load_pin{$instance_name.$pin_name} = $pin_name; ##SAVE ALL LOAD PINS FOR NEG DELAY IN THE ASSOCIATIVE ARRAY##

}

Elsif ($line =~ "CELL" ) {

Print file1 "$line";

$find = 0;

}

Elsif($line =~ "INSTANCE ") ##CHECKING CORRESPONDING INSTANCES AND FIND FLAG = 1 IF FOUND######

{

Print file1 "$line1";

@array2 = split(/\s+/,$line);

$instance_name2 = $array2[1]; ##GETTING THE LOAD INSTANCE NAME FOUND HERE##########

$instance_name2 =~ s/[()]//g;

$instance_definition{$instance_name2} = "$instance_name2" ;

If(exists $load_instance{$instance_name2}) ####COMPARE INSTANCE NAME WITH THAT SAVED IN ASSO ARRAY#####

{

If($load_instance{$instance_name2} eq "$instance_name2")

{$find = 1;}

}

}

Elsif($line =~ "IOPATH" && $find == 1) ##AFTER INSTANCES ARE FOUND CHECKING FOR CORRSPONDING PINS######

{

@array4 = split(/\s+/,$line);

If ($array4[0] =~ "COND" ) { ## Take care of COND statements

$pin_name2 = $array4[3];

} else {

$pin_name2 = $array4[1];

}

If($line =~ "IOPATH" && exists $load_pin{$instance_name2.$pin_name2} ) {

If ( $load_pin{$instance_name2.$pin_name2} eq "$pin_name2" )

{

@array3 = split(/\s+/,$line);

$count3 = @array3 ;

@value_IOPATH = ""; # This is to initialize the array to blank

If ($array3[0] =~ "COND" ) {

For ($j=5; $j<=$count3 ; $j++) {

$value_IOPATH[$j-5] = $array3[$j];

$value_IOPATH_width = @value_IOPATH;

If ($count3 == 6) { #### In case there is only one triplet for COND.*IOPATH

$value_IOPATH[1] = $value_IOPATH[0];

}

#$value1_IOPATH = $array3[5];

#$value2_IOPATH = $array3[6];

}

$constant_fields = 4;

} elsif ($array3[0] =~ "IOPATH") {

For ($k=3; $k<=$count3 ; $k++) {

$value_IOPATH[$k-3] = $array3[$k];

$value_IOPATH_width = @value_IOPATH;

If ($count3 == 4) { #### In case there is only one triplet for IOPATH

$value_IOPATH[1] = $value_IOPATH[0];

}

#$value1_IOPATH = $array3[3];

#$value2_IOPATH = $array3[4];

}

$constant_fields = 2;

}

For($i=0;$i<= $constant_fields;$i++)

{print file1 "$array3[$i] ";}

If( $value_IOPATH[0] =~ "::") ####CORRECT OR ACCOMODATING THE NEG DELAY VALUES HERE #########

{ $value_IOPATH[0] =~ s/[()]//g;

@correct_value1_IOPATH = split(/::/,$value_IOPATH[0]);

If(exists $load_correct_value1_0{$instance_name2}) {

If($load_correct_value1_0{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

If ( abs($load_correct_value1_0{$instance_name2}) < $correct_value1_IOPATH[0] ) { ###the absolute value to negative delay is larger than the timing of load arc. ######

$correct_value1_IOPATH[0] = $correct_value1_IOPATH[0] + $load_correct_value1_0{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}

}

}

If(exists $load_correct_value1_1{$instance_name2})

{ if( $load_correct_value1_1{$instance_name2} < 0.0) {

If ( abs($load_correct_value1_1{$instance_name2}) < $correct_value1_IOPATH[1] ) {

$correct_value1_IOPATH[1] = $correct_value1_IOPATH[1] + $load_correct_value1_1{$instance_name2};}

Else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}}}

Print file1 "($correct_value1_IOPATH[0]::$correct_value1_IOPATH[1])";

}

Elsif( $value_IOPATH[0] =~ ":[^:]") ####CORRECT OR ACCOMODATING THE NEG DELAY VALUES HERE #########

{ $value_IOPATH[0] =~ s/[()]//g;

@correct_value1_IOPATH = split(/:/,$value_IOPATH[0]);

If(exists $load_correct_value1_0{$instance_name2}) {

If($load_correct_value1_0{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

If ( abs($load_correct_value1_0{$instance_name2}) < $correct_value1_IOPATH[0] ) {

$correct_value1_IOPATH[0] = $correct_value1_IOPATH[0] + $load_correct_value1_0{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}

}

}

If(exists $load_correct_value1_1{$instance_name2}) {

If($load_correct_value1_1{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

If ( abs($load_correct_value1_1{$instance_name2}) < $correct_value1_IOPATH[1] ) {

$correct_value1_IOPATH[1] = $correct_value1_IOPATH[1] + $load_correct_value1_1{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}

}

}

If(exists $load_correct_value1_2{$instance_name2}) {

If($load_correct_value1_2{$instance_name2} < 0.0) { # So that only negative delay value triplet is changed in the IOPATH syntax

If ( abs($load_correct_value1_2{$instance_name2}) < $correct_value1_IOPATH[2] ) {

$correct_value1_IOPATH[2] = $correct_value1_IOPATH[2] + $load_correct_value1_2{$instance_name2};

} else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}

}

}

Print file1 "($correct_value1_IOPATH[0]:$correct_value1_IOPATH[1]:$correct_value1_IOPATH[2])";

}

Else{print file1 "$value_IOPATH[0] ";} # This is to print empty brackets in case rise and fall triplets are empty

If( $value_IOPATH[1] =~ "::")

{ $value_IOPATH[1] =~ s/[()]//g;

@correct_value2_IOPATH = split(/::/,$value_IOPATH[1]);

If(exists $load_correct_value2_0{$instance_name2}) {

If( $load_correct_value2_0{$instance_name2} < 0.0)

{ if ( abs($load_correct_value2_0{$instance_name2}) < $correct_value2_IOPATH[0] ) {

$correct_value2_IOPATH[0] = $correct_value2_IOPATH[0] + $load_correct_value2_0{$instance_name2};}

Else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}}}

If(exists $load_correct_value2_1{$instance_name2}) {

If( $load_correct_value2_1{$instance_name2} < 0.0)

{ if ( abs($load_correct_value2_1{$instance_name2}) < $correct_value2_IOPATH[1] ) {

$correct_value2_IOPATH[1] = $correct_value2_IOPATH[1] + $load_correct_value2_1{$instance_name2};}

Else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}}}

If ($correct_value1_IOPATH[0] == $correct_value2_IOPATH[0] && $correct_value1_IOPATH[1] == $correct_value2_IOPATH[1]) { # Print these values ​​only if they are differnet from the already printed values ​​for the IOPATH

} else {

Print file1 " ($correct_value2_IOPATH[0]::$correct_value2_IOPATH[1])";

}

}

Elsif( $value_IOPATH[1] =~ ":[^:]")

{ $value_IOPATH[1] =~ s/[()]//g;

@correct_value2_IOPATH = split(/:/,$value_IOPATH[1]);

If(exists $load_correct_value2_0{$instance_name2}) {

If( $load_correct_value2_0{$instance_name2} < 0.0) {

If ( abs($load_correct_value2_0{$instance_name2}) < $correct_value2_IOPATH[0] ) {

$correct_value2_IOPATH[0] = $correct_value2_IOPATH[0] + $load_correct_value2_0{$instance_name2};}

Else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}}}

If(exists $load_correct_value2_1{$instance_name2}) {

If( $load_correct_value2_1{$instance_name2} < 0.0) {

If ( abs($load_correct_value2_1{$instance_name2}) < $correct_value2_IOPATH[1] ) {

$correct_value2_IOPATH[1] = $correct_value2_IOPATH[1] + $load_correct_value2_1{$instance_name2};}

Else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}}}

If(exists $load_correct_value2_2{$instance_name2}) {

If( $load_correct_value2_2{$instance_name2} < 0.0) {

If ( abs($load_correct_value2_2{$instance_name2}) < $correct_value2_IOPATH[2] ) {

$correct_value2_IOPATH[2] = $correct_value2_IOPATH[2] + $load_correct_value2_2{$instance_name2};}

Else { print "IOPATH delay for $load_pin{$instance_name2.$pin_name2} of $instance_name2 is smaller than the INTERCONNECT delay ";}}}

If ($correct_value1_IOPATH[0] == $correct_value2_IOPATH[0] && $correct_value1_IOPATH[1] == $correct_value2_IOPATH[1] && $correct_value1_IOPATH[2] == $correct_value2_IOPATH[2]) { # Print these values ​​only if they are Differnet from the already printed values ​​for the IOPATH

} else {

Print file1 " ($correct_value2_IOPATH[0]:$correct_value2_IOPATH[1]:$correct_value2_IOPATH[2])";

}

}

Else{print file1 "$value_IOPATH[1] ";} # This is to print empty brackets in case rise and fall triplets are empty

For ($m=2;$m<=$value_IOPATH_width;$m++) {

If (exists $value_IOPATH[$m]) {

$value_IOPATH[$m] =~ s/\)+/\)/; # To account for the brackets

Print file1 " $value_IOPATH[$m]";

}

}

If ($array4[0] =~ "COND" ) { ## Extra bracket for COND statements

Print file1 "))";

} else {print file1 ")";}

}

}

Else

{print file1 "$line1";} #######DUMPING OUT OF SDF IN FILE1############################

}

Else

{print file1 "$line1";}

}

Close(file1);

Close(fileA);

Open(FILEA,$ARGV[0]) || die ("ERROR:: SDF file $ARGV[0] cannot be opened for reading");

Print "#############REPORTING INSTANCES WHOSE DEFINITION IS NOT THERE IN THE SDF############";

While()

{

$line2 = $_;

$line2 =~ s/^\s+//g ;

If ( $line2 =~ "INTERCONNECT.*-[0-9]")

{ @array4 = split(/\s+/,$line2);

$instance_name3 = $array4[2];

$instance_name3 =~ s/\/[^(.*\/)][A-Z0-9a-z_\[0-9\]+]*$//g;

If(exists $instance_definition{$instance_name3})

{}

Else

{print "$line2";}

}

}

Close(fileA);

Print "";

Product categories of Tealight Candle, we are specialized manufacturers from China, Tealight Candle, 10G Color Tealight Candle suppliers/factory, wholesale high-quality products of 12G Poured White Tealight Candle and manufacturing, we have the perfect after-sales service and technical support. Look forward to your cooperation!

12 Gram Tealight Candle,Tealight Candles For Party,Long Burning Tealight Candle,Scented Tealight Candles

Shijiazhuang Zhongya Candle Co,. Ltd. , http://www.zycandlefactory.com