There are many ways to select and classify microcontrollers for specific applications. Starting from the core processor type and memory bus system is one of the common ones. Whether to choose 8-bit, 16-bit, or 32-bit architecture, there are usually the following reference standards: performance level, addressable memory, and system cost.

Customers may sometimes encounter various applications that require a multi-core architecture. This situation means that users not only have to spend more time understanding and mastering various core technologies, peripheral programming techniques and tool usage, but also managing different architecture features. In addition, logistics costs are increased.

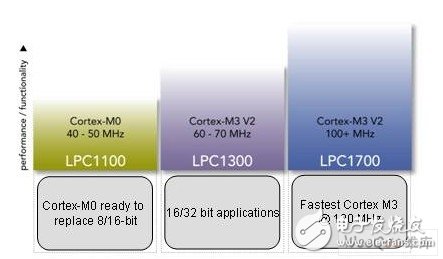

In response to this problem, NXP introduced the LPC1100 series of microcontrollers based on the 32-bit ARM Cortex-M0 processor core. This processor is the smallest of ARM's Cortex-M series and has the advantages of 32-bit architecture performance, low power consumption and ultra-small package. LPC1100 is the latest product of NXP Semiconductors' successful LPC1000 microcontroller series (see Figure 1), which is mainly aimed at the market where 8/16-bit microcontrollers occupy the mainstream low-cost applications.

Figure 1: NXP Cortex-Mx microcontroller family

LPC1100 has the advantages of an ecosystem built around LPC1300 and LPC1700 microcontrollers (both using Cortex-M3 core). From standard interfaces such as UART, I2C and SPI to high-end CAN and USB, the LPC1100 has a complete range of peripherals. The LPC1000 ecosystem includes compilers and debugging tools, various operating systems and software provided by multiple vendors. Since the Cortex-M0 LPC1100 series microcontroller can be upwardly compatible with the M3 core, it can realize development sharing.

This article will focus on the advantages of LPC1100 for several weak applications of the past 8/16-bit microcontrollers. In addition, it will also involve how LPC1100 solves the problems of cost, power consumption and code size, and how to improve the system efficiency of traditional 8/16-bit microcontroller applications.

Energy savingFor home automation applications such as door, window or lighting control, sensors are mainly used to connect to the internal buses of the home automation system. These buses and sensors obtain current from a dedicated DC circuit and are in working mode most of the time. The outstanding low power consumption characteristics of LPC1100 in working mode provide an ideal choice for such applications.

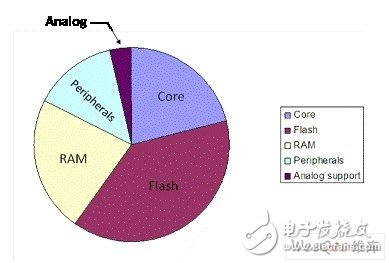

Figure 2 is a typical application example of executing code from flash memory and operating dynamic data in RAM, showing the power consumption of several internal system modules of the LPC1100 in normal operating mode.

Figure 2: Power consumption of each module at 20MHz core frequency

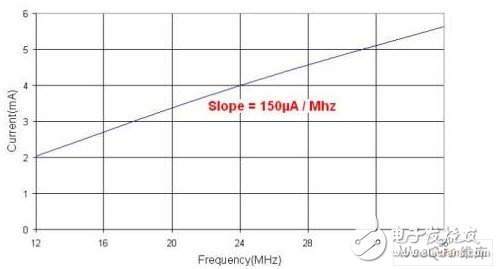

In the total current consumption, the Cortex-M0 core and internal storage system account for the largest proportion. Although the processing power of the Cortex-M0 core is super strong, the average power consumption of the LPC1100 using this core is only about 150μA/MHz when running in an infinite loop.

Figure 3 Power consumption of executing code from flash memory in normal operating mode

It is expected that after the launch of the new low-power (LP) LPC1100 product, the low-power performance of the existing LPC1100 microcontroller will be further improved. Power consumption in working mode is expected to drop to around 130uA/MHz.

In addition, because the M0 core uses a 32-bit architecture, the current utilization efficiency is higher than that of the 8/16-bit architecture. For performing the same computing task, the actual operating speed of the M0 core can be 2-4 times lower than that of an 8/16-bit microcontroller, so the power consumption is much lower than an 8/16-bit microcontroller.

For "deep sleep" or "deep power-down" modes, the powerful processing capabilities of the Cortex-M0 core are also useful. Compared with the 8/16-bit architecture, the 32-bit architecture takes less time to perform tasks, so the microcontroller is more It will run in low power mode for many times. The new LP series products will significantly reduce the power consumption of deep sleep mode (2uA) and deep power-down mode (220nA).

BLPC1100 is very suitable for simultaneously processing the basic tasks of the microcontroller (MCU) and various operands (8-bit, 16-bit or higher) operations. Embedding a fast 32-bit Cortex-M0 core (maximum frequency 50MHz) and maintaining the flexibility of microcontroller operation and programming (Cortex-M0 core can completely use C language) is the best solution to replace the 16-bit hybrid system.

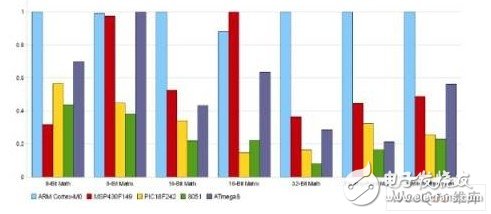

The Cortex-M0 microcontroller can easily surpass high-end 8/16-bit microcontrollers. The Cortex-M0 core has a rated processing capacity of up to 0.8DMIPS/MHz, which is 2-4 times that of high-end 8/16-bit microcontrollers. Because DMIPS and MIPS sometimes cannot accurately reflect the performance of user devices, Figure 4 shows the relative performance of each device based on some common test benchmark procedures. Most commonly used Cortex-M0 Thumb2 instructions are single-cycle instructions, and all 8-bit, 16-bit and 32-bit data transfers are completed in one instruction cycle. It usually takes a long time to process long word multiplication in 8-bit and 16-bit microcontrollers. However, since the Cortex-M0 core is a 32-bit architecture, NXP uses a 32x32-bit hardware multiplier in the LPC1100. Through the MULS instruction, it successfully The multiplication of two 32-bit words is completed in one instruction cycle.

Figure 4 Cortex-M0 relative performance

The division operation can be completed by software, and Cortex-M0 has the same excellent performance for various operand division operations.

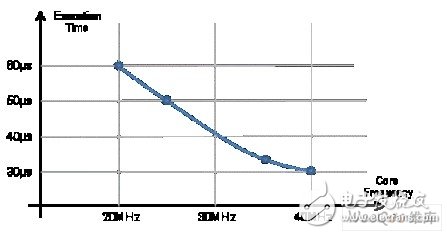

For specific applications, complex calculations usually involve multiple additions, multiplications, and divisions. Figure 5 shows the execution time of a complex calculation. The execution condition is to execute the code from the flash memory, using floating-point operands to perform 5 multiplications, 5 additions, and 1 division calculations. For floating-point operations, the C language code can be optimized by a specific Cortex-M0 math library function.

Figure 5: Floating point calculation time example

Re-optimizing some important functions from the math library to RAM can further improve performance. These library functions should be called in RAM to avoid long branches in the allocation process from ROM pages to RAM pages to shorten the execution time.

Interrupt handlingThe performance of a microcontroller depends not only on the execution speed, but also an important aspect of interrupt handling. Interrupt performance is generally reflected by delay time and jitter. Delay refers to the time from the occurrence of an interrupt event to the entry of the interrupt service routine, and jitter is used to describe the change in delay.

Cortex-M0 minimizes the delay time by tightly coupling the interrupt controller and the core. The highest priority interrupt delay time is fixed at 16 clock cycles. The interrupt controller can support up to 32 different interrupt sources, including a non-maskable interrupt input. LPC1100 provides special interrupt vectors for various interrupt events, and any interrupt will automatically allocate a special interrupt service routine (ISR, Interupt Service Routine) without software processing.

In order to shorten the delay time of nested interrupts, LPC1100 adopts an integrated mechanism. If the high-priority interrupt arrives before the low-priority interrupt enters the service routine, it can avoid re-stacking. In addition, the LPC1100 also supports tail chaining, which can directly enter the ISR by superimposing the abnormal stacking sequence and the subsequent abnormal stacking sequence to shorten the delay time.

System costThere are several factors that affect the total cost of the system. For small systems, the kernel and memory account for the largest proportion.

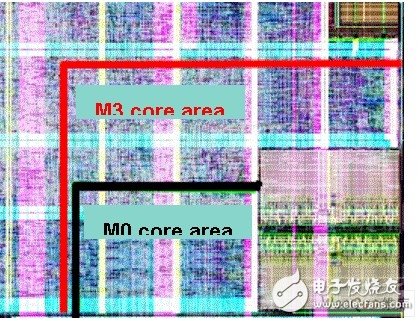

Core size: Cortex-M0 core is developed specifically for low-cost applications, mainly for the previous 8/16-bit small microcontroller architecture market. The size of the Cortex-M0 core is only 1/4 of the Cortex-M3, see Figure 6. For small systems with fewer peripherals and limited Flash space, a smaller core can reduce the overall size of the chip. The number of Cortex-M0 logic gates has reached the level of the most classic 8-bit core, but it brings better processing power and provides upward compatibility for the more powerful Cortex-M series processors.

Figure 6 Cortex-M0 core size

Small footprint of flash memory: The size of flash memory required to store application code is another important factor that affects the total cost of the system. Considering that 32-bit instructions are more powerful than 8-bit instructions, and can replace multiple 8-bit instructions at a time, it can be assumed that the application code size is basically the same (not including the constant table). However, according to the actual test results of the 8-bit code entered into the LPC1100, the application code size is much smaller, and can even reach less than 50%.

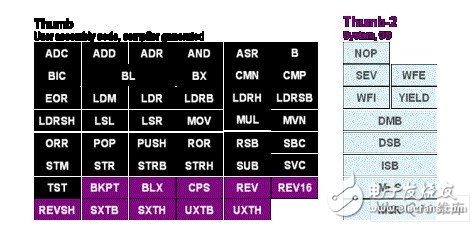

ARM Cortex-M0 executes the Thumb instruction set, including a small number of 32-bit instructions using Thumb-2 technology, see Figure 7. The Thumb instruction set is a subset of the instruction set supported by ARM Cortex-M3 and ARM Cortex-M4, and is upwardly compatible with its binary code.

Combining ARM7TDMI's 16-bit Thumb instructions and some of the powerful 32-bit instructions of Thumb-2 can improve code density. The compiler will choose whether to use 16-bit or 32-bit instructions, and the two can completely coexist in the final code. During operation, the system can achieve seamless switching between 16-bit and 32-bit codes, without the need for special instructions as when using ARM7TDMI. The following table is a complete instruction set of Cortex-M0.

Figure 7: Cortex M0 instruction set

Overall, LPC1100 has a strong competitiveness in the low-cost MCU market, and its outstanding flexibility and powerful performance will become the most powerful competitor in various application fields where 8-bit and 16-bit architectures dominate. LPC1100 supports ultra-small packages (16-pin CSP, 2.5 x 2.5mm) and easy-to-operate HVQFN and LQFP packages. All products in this series support common peripherals such as UART, I2C and SPI, and can reuse the drivers of these peripherals on other products in the LPC1000 series. In addition, LPC1100 also supports high-end peripherals such as USB and CAN, and its driver code is embedded in the ROM mask, so the Flash memory can be completely used for users' own applications.

Special Wire Rope For Port And Engineering Machinery

special wire rope, wire rope for port machinery, wire rope for engineering machinery

ROYAL RANGE INTERNATIONAL TRADING CO., LTD , https://www.royalrangelgs.com