Recently, at the Hot Chips conference in California, Baidu released the XPU, a 256-core, FPGA-based cloud computing acceleration chip, and the partner is Xilinx. Baidu also revealed details about the more architectural aspects of the chip at this conference.

In the past few years, Baidu has made good progress in the field of deep learning, especially in the field of deep learning based on GPU. Moreover, Baidu is also developing a new processor called XPU.

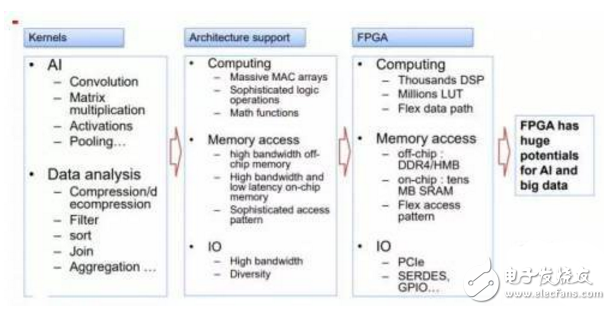

Baidu explains the situation of AI and data analysis workloads on FPGA

Baidu researcher Ouyang Jian said that Baidu designed the chip architecture to highlight diversity, focusing on computationally intensive, rule-based tasks while ensuring maximum efficiency, performance and flexibility. Today, he released the XPU with the people from the FPGA vendor Xilinx at the Hot Chips conference.

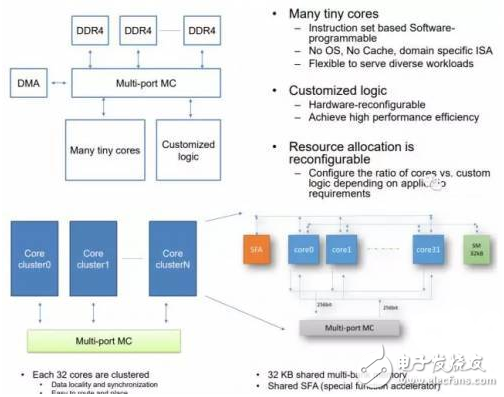

The goal of XPU is to balance performance and efficiency and handle diverse computing tasks. The FPGA accelerator itself is very good at handling certain computing tasks, but as many small cores are intertwined, the level of diversity will increase.

Ouyang Jian said: "FPGA is efficient, can focus on specific computing tasks, but lacks programmability. Traditional CPUs are good at general computing tasks, especially rule-based computing tasks, and very flexible. GPU is aimed at parallel computing, so there are Very powerful performance. XPU focuses on compute-intensive, rule-based, diverse computing tasks, hoping to increase efficiency and performance, and bring CPU-like flexibility."

At present, the lack of XPC is still the programmability, and this is a common problem when it comes to FPGA. So far, XPU has not provided a compiler. However, Ouyang Jian said that the team will soon develop a compiler.

Ouyang Jian also said that in order to support matrix, convolution, and other large and small cores, we need a large mathematical array with high bandwidth and low latency memory, as well as high bandwidth I / O interface. The DSP unit of the XPU in the FPGA provides parallel processing capabilities. The off-chip DDR4 and HBM interfaces optimize data transfer, while the on-chip SRAM provides the necessary memory features.

In the Micro Benchmark test, the XPU is similar in efficiency to the x86 core for computationally intensive, conventional memory access computing tasks. For computing tasks of data synchronization, the scalability of the XPU should be further optimized. For computing tasks without data synchronization, the scalability of the XPU is linear with the number of cores.

This is where the problem lies. As mentioned earlier, XPU still does not have a compiler. This processor is implemented on an FPGA and provides instructions through custom logic. These small cores are similar to CPUs, developers can only use assembly language, and all execution is controlled by the host. The entire process involves splitting the computational tasks, writing the XPU code, and calling specialized logic functions to compile and run on the Linux platform.

The XPU has 256 cores and integrates a shared memory for data synchronization. All cores run at 600MHz.

Ouyang Jian said: "In Baidu, we have been using FPGA for many years. We have a large number of FPGAs in our data centers, cloud computing platforms and autopilot projects. We understand the advantages and disadvantages of FPGAs and how to optimize them. With the large core of XPU We focus on diverse computing tasks."

Last year, some media reported on the SQL accelerator based on Baidu deep learning SDA. The data flow at the time was based on the SA architecture. According to Ouyang Jian, this is also the core of XPU's memory bandwidth and latency advantages.

Ouyang Jian also showed some benchmark tests completed this year, but the information is very rough. However, this is just Baidu’s first public display of XPU.

If XPU is proven to work with AI, data analysis, cloud computing, and driverless, then Baidu may need to develop XPU with ASIC technology.

ZGAR Aurora 1200 Puffs

ZGAR electronic cigarette uses high-tech R&D, food grade disposable pod device and high-quality raw material. All package designs are Original IP. Our designer team is from Hong Kong. We have very high requirements for product quality, flavors taste and packaging design. The E-liquid is imported, materials are food grade, and assembly plant is medical-grade dust-free workshops.

Our products include disposable e-cigarettes, rechargeable e-cigarettes, rechargreable disposable vape pen, and various of flavors of cigarette cartridges. From 600puffs to 5000puffs, ZGAR bar Disposable offer high-tech R&D, E-cigarette improves battery capacity, We offer various of flavors and support customization. And printing designs can be customized. We have our own professional team and competitive quotations for any OEM or ODM works.

We supply OEM rechargeable disposable vape pen,OEM disposable electronic cigarette,ODM disposable vape pen,ODM disposable electronic cigarette,OEM/ODM vape pen e-cigarette,OEM/ODM atomizer device.

Aurora 1200 Puffs,ZGAR Aurora 1200 Puffs Pod System Vape,ZGAR Aurora 1200 Puffs Pos Systems Touch Screen,ZGAR Aurora 1200 Puffs Disposable Vape Pod System,1200Puffs Pod Vape System

ZGAR INTERNATIONAL(HK)CO., LIMITED , https://www.zgarpods.com